## **ELECTRONICS AND COMMUNICATION SYSTEMS**

51. Draw the circuit diagram for studying the characteristics of an *n-p-n* transistor in common emitter configuration. Sketch the typical (i) input and (ii) output characteristics in CE configuration

[All India 2008, 2014, Delhi 2009, 2009C, 2010C, 2013C, Foreign 2012]

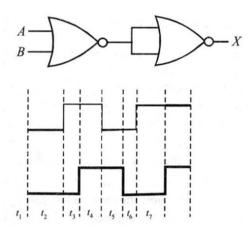

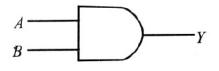

52. Draw the output waveform at X, using the given inputs, A and B for the logic circuit shown below.

[Delhi 2008, 2011]

53. Draw a simple circuit of a CE transistor amplifier.

[Foreign 2008, Delhi 2012]

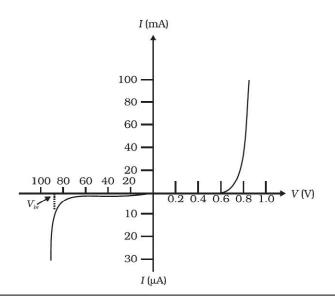

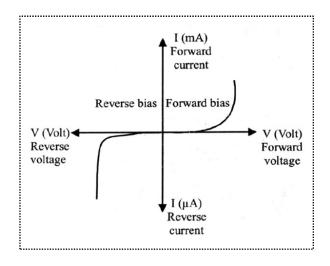

54. Draw V-I characteristics of a p-n junction diode.

[All India 2009, 2011, 2013]

55. Draw the logic circuit of a NAND gate.

Draw the logic circuit of AND gate.

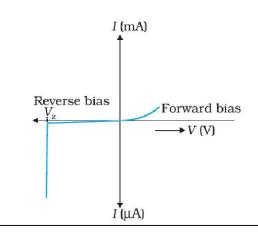

Draw I-V characteristics of zener diode.

56.

57.

[All India 2009, Foreign 2011]

[All India 2009, Foreign 2011]

[Delhi 2009]

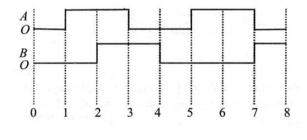

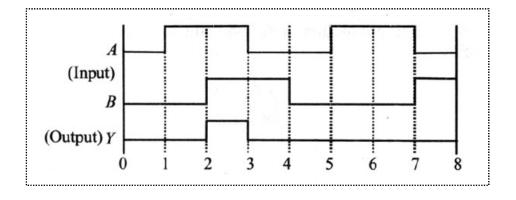

58. Sketch the output wavefrom from an AND gate for the input *A* and *B* shown in the figure.

[Delhi 2009]

59. Draw the circuit diagram showing how a *p*-*n* junction diode is (i) forward biased, (ii) reverse biased

[All India 2010, 2011c]

60. Draw the circuit diagram of an illuminated photodiode in reverse bias. [Delhi 2010]

| 61. Draw the logic circuit of a NOT gate.                                                                                                             |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [Foreign 2011]                                                                                                                                        |  |

| 62. Show how intensity of current varies with illumination intensity in a photodiode.                                                                 |  |

| Plot a graph showing variation of current versus voltage for the material GaAs.                                                                       |  |

| [Delhi 2014]                                                                                                                                          |  |

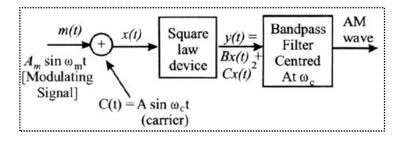

| 4. Draw a labelled block diagram of a simple modulator for obtaining an AM signal.                                                                    |  |

| [All India 2008, Delhi 2008C, 2009, Foreign 2010]                                                                                                     |  |

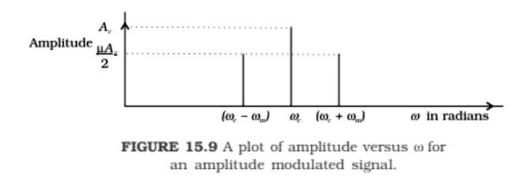

| Draw a plot of the variation of amplitude versus $\omega$ for an amplitude modulated wave.                                                            |  |

| [Delhi 2008]                                                                                                                                          |  |

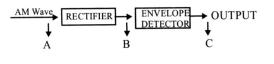

| Draw block diagram of a detector for AM waves?                                                                                                        |  |

| [Delhi 2008C, 2013C]                                                                                                                                  |  |

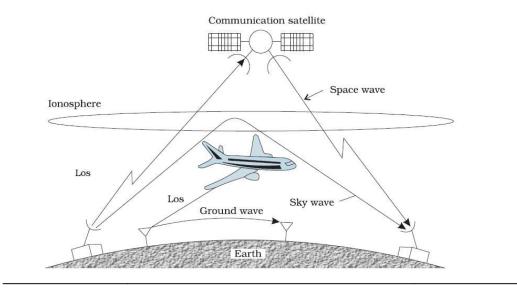

| <ul><li>67. Draw a schematic diagram showing the</li><li>(i) ground wave (ii) sky wave and (iii) space wave propagation modes for em waves.</li></ul> |  |

| [All India 2011C, Delhi 2012]                                                                                                                         |  |

| () Drow diagram for following:                                                                                                                        |  |

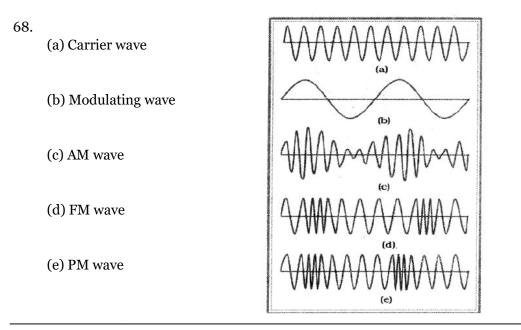

68. Draw diagram for following:(a) Carrier wave(c) AM wave(e) PM wave

(b) Modulating wave(d) FM wave

69. Figure shows the block diagram of a detector for AM signal. Draw the waveforms for the (i) input AM wave at A (ii) output B at rectifier and (iii) output signal at C.

[All India 2013C]

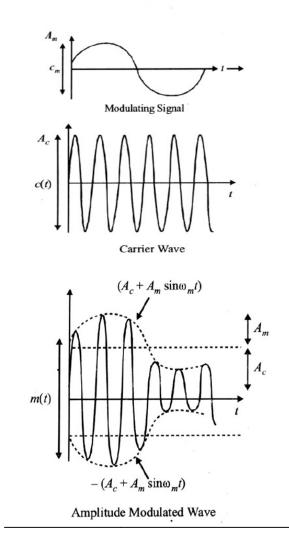

- 70. Draw a schematic sketch showing how amplitude modulated signal is obtained by superposing a modulating signal over a sinusoidal carrier wave. [All India 2014, Delhi 2013]

- 71. Draw the necessary energy band diagrams to distinguish between conductors, semiconductors and insulators. How does the change in temperature affect the behavior of these materials? Explain briefly. [All India 2015]

- 72. Draw a circuit diagram of a transistor amplifier in CE configuration. [Delhi 2015]

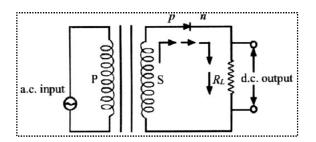

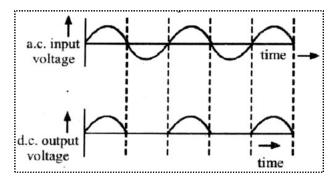

73. Draw the circuit diagram of a half wave rectifier.

[All India 2013C, 2016]

- 74. Draw the circuit diagram for studying the input and output characteristics of n-p-n transistor in common emitter configuration. [Delhi 2016]

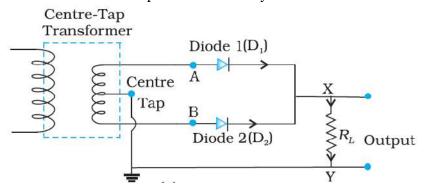

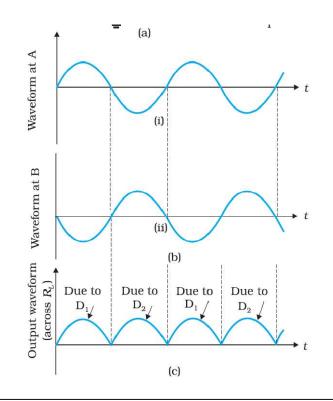

- 75. Draw the circuit diagram of a full wave rectifier.

[All India 2017]

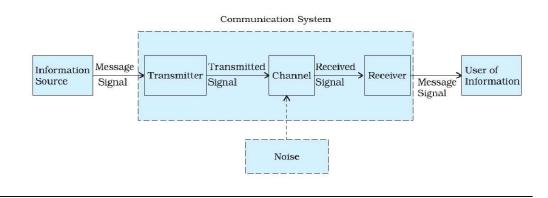

76. Draw a block diagram of a generalized communication system. [All India 2017]

## **SOLUTIONS**

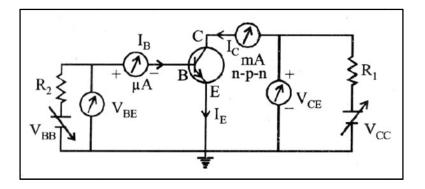

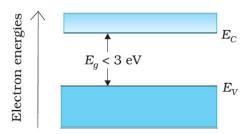

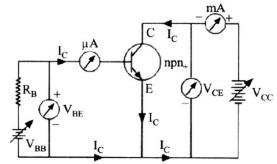

- 51. The circuit diagram of n-p-n transistor in CE configuration is as shown below

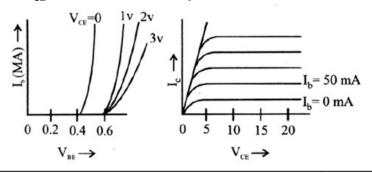

- (i) Input characteristics: It is a graph between base voltage  $V_B$  and the base current  $I_B$  for a constant value of collector voltage  $V_C$ .

- (ii) Output characteristics: It is a graph between collector voltage  $V_{CE}$  and collector current Ic for a constant value of base current  $I_B$ .

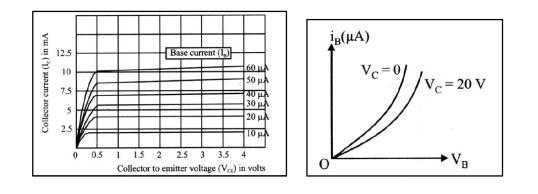

52. Equivalent gate is OR gate. Logic symbol of OR gate and the output waveform . Symbol of OR gate.

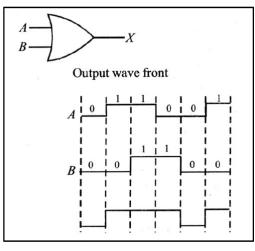

53. Circuit diagram of a common emitter transistor amplifier

54. *V-I* characteristic of a *p-n* junction diode.

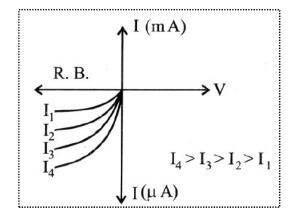

55. Logic circuit of NAND gate.

56. Logic circuit of a AND gate

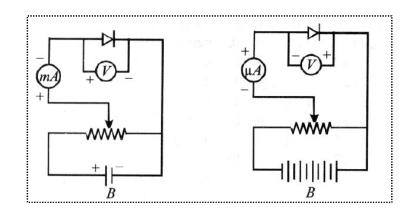

57. Zener diode is operated in the reverse breakdown region. The voltage across it remains constant.V-I characteristic of a zener diode

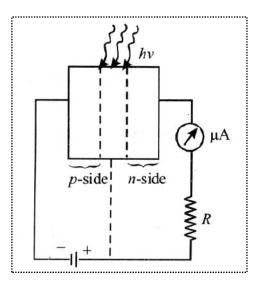

58. The output for an AND gate is given as

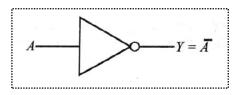

| -           | 0             | e                  |

|-------------|---------------|--------------------|

| For 0 to 1, | A = 0, B = 0, | therefore, $y = 0$ |

| For 1 to 2, | A = 1, B = 0, | therefore, $y = 0$ |

| For 2 to 3, | A = 1, B = 1, | therefore, $y = 1$ |

| For 3 to 4, | A = 0, B = 1, | therefore, $y = 0$ |

| For 4 to 5, | A = 0, B = 0, | therefore, $y = 0$ |

| For 5 to 6, | A = 1, B = 0, | therefore, $y = 0$ |

| For 6 to 7, | A = 1, B = 0, | therefore, $y = 0$ |

| For 7 to 8, | A = 0, B = 1, | therefore, $y = 0$ |

|             |               |                    |

- 59. Circuit diagram of (i) forward biased and (ii) reverse biased p-n junction diode .

- (i) Circuit diagram of forward biased p-n junction diode.

(i) Circuit diagram of reverse biased p-n junction diode

60. Circuit diagram of illuminated photodiode in reverse bias .

61. Logic circuit of a NOT gate.

62. Graph showing variation of intensity of current with illumination intensity.

63. Current – Voltage characteristic graph for GaAs:

64. Block diagram of a simple modulator

65. A plot of amplitude versus  $\omega$  for an amplitude modulated wave.

66. The block diagram is as shown below:

## 67. Schematic diagram of showing propagation of

(i) Ground wave (ii) Sky wave (iii) Space wave

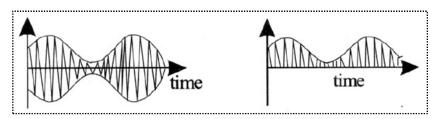

- 69. Wave forms for the:

- (i) Input AM wave at A (ii) Output B at the rectifier

(iii) Output signal at C

70. Amplitude modulated signal is obtained by superposing a modulating signal over a sinusoidal carrier wave is shown in the figure given below

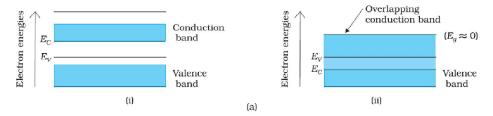

71. In conductors, the conducting and the valence band overlap each other. As the temperature increases, the conductivity of the conductors decreases due to increase in the thermal motion of the free electrons. Energy band diagram for a conductor

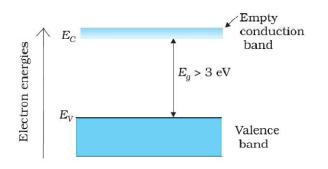

**Energy band diagram for an insulator**

The valance band is completely filled and the conduction band is empty. The energy band gap of the insulator is quite large. So, on increasing the temperature, the electrons of the valence band are not able to reach the conduction band. Therefore, electrical conduction in these materials is almost impossible.

## **Energy band diagram for a semiconductor**

In semiconductor, the valence band is fully filled and the conducting band is empty but the energy gap between conduction band and valence band is quite small. At zero K, electrons are not able to cross even this small energy gap and, therefore, the conduction band remains totally empty. At room temp., some electrons in the valence band acquire thermal energy greater than energy band gap, which is < 3 eV and jump over to the conduction band where they are free to move under the influence of even a small change in the temperature. As the temperature increases more and more electrons crosses the band gap and therefore conductivity increases.

72. The circuit diagram of an n-p-n transistor amplifier in CE configuration is given below:

73. The circuit diagram for a half wave rectifier is shown below:

Working: During the positive half cycle of the input a.c., the p-n junction is forward biased i.e., the forward current flows from p to n and the diode offers a low resistance path to the current. Thus, we get output across-load i.e. a.c input will be obtained as d.c output.

During the negative half cycle of the input a.c., the p-n junction is revered biased i.e., the reverse current flows from n to p, the diode offers a high resistance path to the current. Thus, we get no output across-load. 74. Circuit diagram for studying the input and output characteristic Input characteristic. Curve is drawn between base current  $I_b$  and emitter

base voltage  $V_{EB}$  at constant collector emitter voltage  $V_{CE}$ Output characteristic. Variation of collector current  $I_C$  with  $V_{CE}$  can be noticed for  $V_{CE}$  between 0 to 1 volt only.

75. P-N junction diode as a full wave rectifier: The circuit uses two diodes connected to the ends of a centre tapped transformer. The voltage rectified by the two diodes is half of the secondary voltage i.e., each diode conducts for half cycle of input but alternately so that net output across load comes as half sinusoids with positive values only.

For positive cycle diode  $D_1$  conducts (FB) but  $D_2$  is being out of phase is reverse biased and does not conduct. Thus output across  $R_L$  is due to  $D_1$  is R.B. but  $D_2$  is F.B. and conducts as with respect to centretap point A is negative but B is positive. Therefore output across  $R_L$  is due to  $D_2$ .

76. Block diagram of a generalized communication system: