# Inction Field Effect ransistors

- FET is a unipolar and voltage controlled device.

- The terminals drain, gate and source of a FET are identical to collector base and emitter of a BJT.

- Since the input function is reverse biased in JFET, the current drawn is very small and so input impedance is very high.

- Less noisy device due to absence of minority carriers.

- Excellent thermal stability due to absence of leakage current.

- FET is considered as excellent signal chopper because of zero offset voltage.

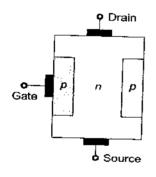

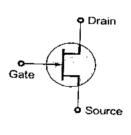

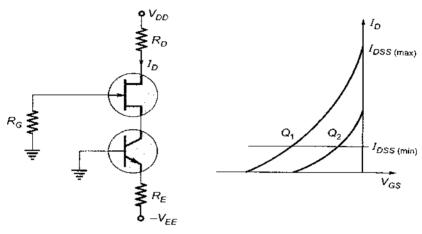

# Circuit Diagram and Symbol

#### **Parameters**

#### **Drain current**

$$I_D = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_p} \right]^2$$

In saturation region

where,

$I_D$  = Drain current

$I_{\mathrm{DSS}} = \mathrm{Maximum}\,\mathrm{value}\,\mathrm{of}\,\mathrm{current}\,\mathrm{when}\,\,V_{\mathrm{GS}} = 0$

$V_n$  = Pirch off voltage

$V_{GS}$  = Gate to source voltage

#### **Drain resistance**

$$r_d = \frac{\Delta V_{DS}}{\Delta I_{DS}} \bigg|_{V_{GS} = \text{constant}}$$

Note:

$r_d$  ranges from 100 k $\Omega$  to 500 k $\Omega$ .

#### Transconductance

$$g_m = \frac{\Delta I_D}{\Delta V_{GS}}\Big|_{V_{DS\text{-constant}}}$$

Note

$g_m$  ranges from 0.1 mS to 10 mS.

In saturation region

$$g_m = -\frac{2I_{DSS}}{V_p} \left( 1 - \frac{V_{GS}}{V_p} \right) = -\frac{2}{V_p} \sqrt{I_D.I_{DSS}}$$

Also,

$$g_m = g_{mo} \left( 1 - \frac{V_{GS}}{V_{p}} \right)$$

where,

$$g_{mo} = -\frac{2J_{DSS}}{V_p}$$

= maximum value of transconductance

#### **Amplification Factor**

$$\mu = \left(\frac{\Delta V_{OS}}{\Delta V_{GS}}\right)_{I_D} = \text{Constant}$$

Note:

- $\mu$  ranges from 2.5 to 150.

- Relation between  $\mu$ ,  $r_d$  and  $g_m$  is  $\mu = r_d \cdot g_m$

Remember:

If two FETs are connected in parallel having transconductance  $g_{m_1}$  and  $g_{m_2}$ , drain resistance  $r_{d_1}$  and  $r_{d_2}$ , amplification factor  $\mu_1$  and  $\mu_2$  then

Effective transconductance  $g_m = g_{m_1} + g_{m_2}$ .

Effective drain resistance  $r_d = r_{d_1} || r_{d_2}$ .

Effective amplification factor  $\mu = \frac{\mu_1 r_{d_2} + \mu_2 r_{d_1}}{\mu_1 + \mu_2}$ .

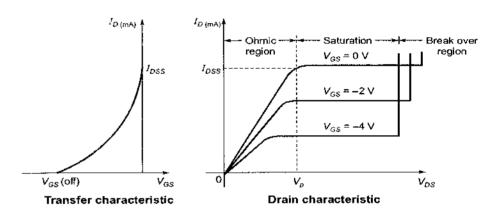

#### Characteristics of JFET

Remember:

When FET is operated below pinch-off voltage  $(V_p)$ , it acts as a voltage variable resistor.

.....

## **FET Amplifiers**

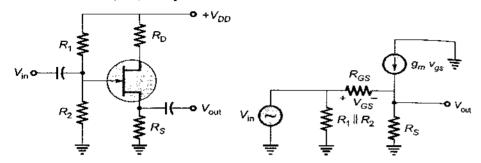

#### **Common Source Amplifier**

**AC output voltage**

$$V_{\rm out} = -g_m V_{\rm GS} R_{\rm D}$$

#### Unloaded voltage gain

$$A = -G_{m}R_{D}$$

#### Common Drain (CD) Amplifier

AC input voltage

$$V_{\rm in} = (1 + g_m R_S) V_{\rm GS}$$

AC output voltage

$$V_{\rm out} = g_m V_{\rm GS} R_s$$

Unloaded voltage gain

$$A = \frac{R_S}{R_S + 1/g_m} \stackrel{\text{def}}{=} 1 \qquad \dots \text{(as } R_S >> 1/g_m)$$

**Output impedance**

$$Z_{\text{out}(\text{source})} = 1/g_m$$

;  $Z_{\text{out}} = R_S \parallel 1/g_m$

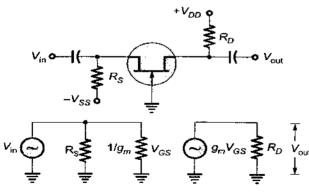

#### Common Gate (CG) Amplifier

AC equivalent circuit

**AC input voltage**

$$V_{\rm in} = V_{\rm GS}$$

AC output voltage

$$V_{\rm out} = g_m V_{\rm GS} R_D$$

Unloaded voltage gain

$$A=g_mR_D$$

Input impedance

$$Z_{\rm in} = \frac{1}{g_{m}}$$

DC on-state resistance

$$r_{DS(on)} = \frac{V_{DS}}{I_D}$$

where,

$r_{DS(on)} = DC$  resistance in saturation region

$v_{DS}$  = DC drain-source voltage

$I_D$  = DC drain current

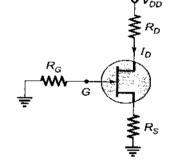

# **FET Biasing Circuit**

## Self bias circuit

Gate to source voltage

$$V_{GS} = -I_D R_s$$

Source resistance

$$R_s = -V_p/I_{DSS}$$

Note:

Q-point is the interaction between the tranconductance and the self bias line.

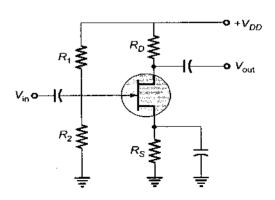

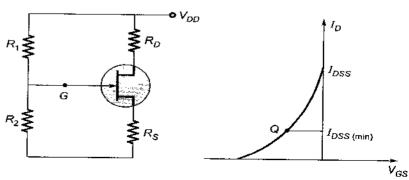

#### Voltage divider/Source bias circuit

#### Drain current

$$I_D = \frac{V_{Th} - V_{GS}}{R_s}$$

where,  $V_{Th} = \left(\frac{R_2}{R_1 + R_2}\right) V_{DD}$

#### Current source bias circuit

#### Collector current

$$I_C = I_D = \frac{V_{EE} - V_{BE}}{R_E}$$