# **DIGITAL LOGIC TEST 2**

# Number of Questions: 25

*Directions for questions 1 to 25:* Select the correct alternative from the given choices.

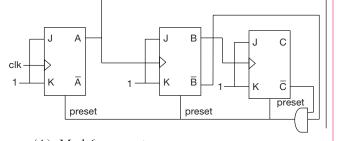

1. The ripple counter shown in figure works as a:

- (A) Mod-6 up counter

- (B) Mod-5 up counter

- (C) Mod-5 down counter

- (D) Mod-6 down counter

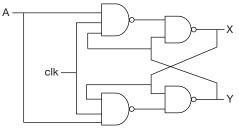

- 2. Consider the given circuit:

In this circuit, the race around condition

- (A) does not occur

- (B) occurs when clk = 0

- (C) occurs when clk = 0, A = 1 and X = Y = 1

- (D) occurs when clk = 1, A = 1

- **3.** Three, modulo-4 counters are cascaded together then the resultant counter modulus is

- (A)  $3 \times 4$  (B)  $3^4$ (C)  $4 \times 4 \times 4$  (D) 3 + 4

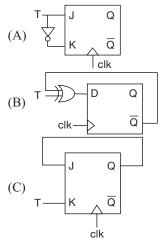

- 4. Which of the following flip flop configuration works as *T* flip flop:

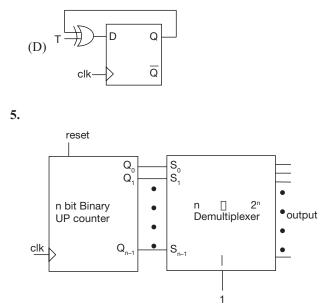

'*n*' bit Binary UP counter is connected to  $n \times 2^n$  Demultiplxer with input I = 1, as shown in the figure.

If the counter starts from reset, the above configuration works as

- (A) Modulo  $-2^n$  twisted ring counter

- (B) Modulo -n ring counter

- (C) Modulo -2n Johnson counter

- (D) Modulo  $-2^n$  ring counter

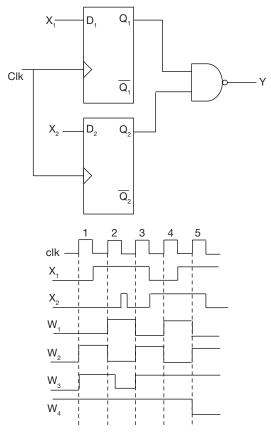

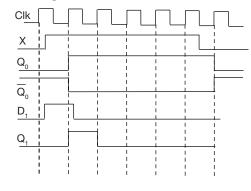

- 6. Consider the following circuit with initial state  $Q_0 = Q_1$ = 0. The *D* flip flops are positive edge triggered.

Consider the following timing diagrams of *X* and clk. Which one is the correct wave form of *Y*?

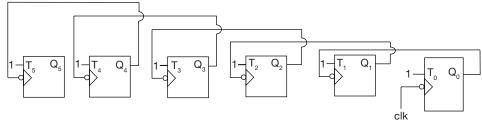

7. Six JK Flip flops are cascaded to form the circuit shown in figure. Clock pulses at a frequency of 128 kHz are applied as shown, The frequency (in kHz) of the wave form at  $Q_4$  is \_\_\_\_\_.

#### Section Marks: 30

| (A) | 32 kHz | (B) | 16 kHz |

|-----|--------|-----|--------|

| (C) | 8 kHz  | (D) | 4 kHz  |

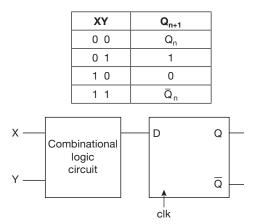

**8.** The following truth table has to be realized with *D* flip flop.

Then what is the equation of combinational logic circuit output in terms of *X*, *Y* and  $Q_n$ ?

- (A)  $D = \overline{X}Q_n + Y\overline{Q}_n$  (B)  $D = X\overline{Q}_n + \overline{Y}Q_n$ (C)  $D = XY + Q_n$  (D)  $D = (X + Y) + Q_n$

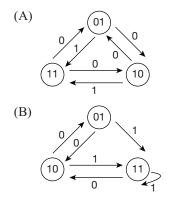

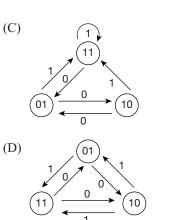

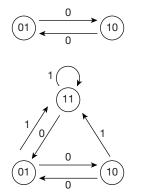

- **9.** A clocked sequential circuit has 3 states *A*, *B*, *C* and 1 input *X*. As long as input X = 0, the circuit alternates between states *A* and *B*, if input X = 1 (either in state *A* or *B*), The circuit goes to state *C* and remain in state *C* as long as X = 1, from state *C*, circuit returns to state *A* when input X = 0, and then a repeats its behavior. Assume A = 01, B = 10, C = 11 the state diagram will be:

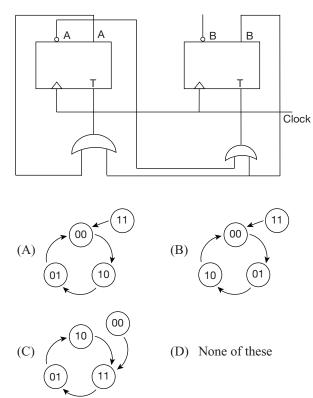

**10.** Find the state (*AB*) diagram for the following sequential circuit?

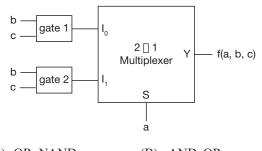

11. The Boolean function  $f(a, b, c) = a^1 b + b^1 c + ac^1$  has to be implemented by the following  $2 \times 1$  multiplexer then the gate 1 and gate 2 are respectively?

- (A) OR, NAND(B) AND, OR(C) NOR, AND(D) NAND, OR

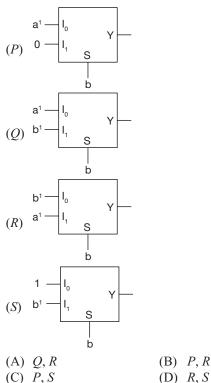

- **12.** Which of the following multiplexer implements 2 input NAND gate?

13. The output of the following Demultiplexer circuit is:

14. An  $8 \times 1$  multiplexer has inputs *A*, *B*, *C* connected to the selection inputs  $S_2$ ,  $S_1$  and  $S_0$  respectively. The data

inputs  $I_0$  through  $I_7$  are as follows.  $I_1 = I_2 = 0$ ;  $I_3 = I_5 = I_7 = 1$ ;  $I_0 = I_4 = D$ ; and  $I_6 = D^1$  then the Boolean function that the multiplexer implements is?

- (A)  $AB + BC + A\overline{C}D + \overline{B}\overline{C}D$

- (B)  $AC + BD + A\overline{B}D + B\overline{C}\overline{D}$

- (C)  $\overline{B}\overline{C}D + AB\overline{D} + BC + AC$

- (D)  $A\overline{B}D + \overline{B}\overline{C}D + A\overline{C} + BC$

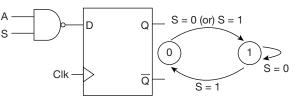

- 15. The digital circuit shown in the figure satisfies the given state diagram, when Q, is connected to input A of NAND gate

Suppose the NAND gate is replaced by an OR gate which are of the following options preserves the state diagram.

- (A) input A is connected to Q

- (B) input A is connected to 1 and S is complemented

- (C) input A is connected to S

- (D) input A is connected to  $\overline{Q}$  and S is complemented

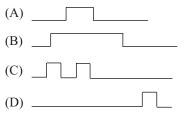

- 16. In the circuit shown choose the correct timing diagram of output *Y* from the given wave forms  $W_1$ ,  $W_2$ ,  $W_3$  and  $W_4$

(A)

$$W_1$$

(B)  $W_2$

(C)  $W_3$  (D)  $W_4$

18. Suppose only one multiplexer and one inverter allowed to be used to implement any Boolean function of *n* variables. What is the minimum size of the multiplexer needed?

| (A) $2^n$ line to 1 line     | (B) $2^{n-1}$ line to 1 line |

|------------------------------|------------------------------|

| (C) $2^{n-2}$ line to 1 line | (D) $2^{n+1}$ line to 1 line |

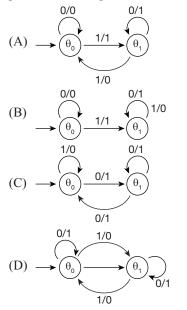

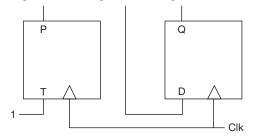

19. Which one of the following state diagram represents finite state machine, which takes as input a binary number from the least significant bit and computes 2's complement of the input number.

20. The following arrangement of Master-slave flip flips has the initial state of P, Q as 0, 1 respectively after the 3 clock pulses, the output states P, Q is:

| (A) | 1,0  | (B) | 0, 1 |

|-----|------|-----|------|

| (C) | 1, 1 | (D) | 0,0  |

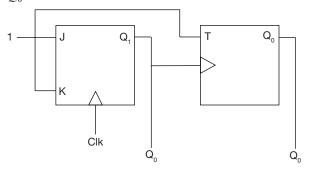

21. In the sequential circuit below, if the initial value of the output  $Q_1 Q_0$  is 00, what are the next four values  $Q_1$ ,  $Q_0?$

- (A) 01, 10, 11, 00

- (B) 11, 10, 01, 00

- (C) 01, 11, 10, 00

- (D) 10, 11, 01, 00

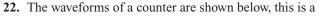

- (A) synchronous BCD counter

- (B) ripple counter

- (C) ring counter

- (D) twisted ring counter

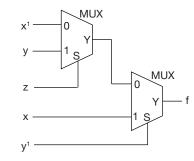

- 23. Consider the circuit, here, which are the following options correctly represents f(x, y, z)

- (A)  $x^{1}y^{1} + xy + xz$ (B)  $xy^{1} + x^{1}y + xz$ (C)  $x^{1}y + xy^{1} + y^{1}z$

- (D)  $xy + x^{1}y^{1} + xyz$

# 3.14 | Digital Logic Test 2

- 24. The outputs Q and  $\overline{Q}$  of a master slave SR flip flop are connected to its R and S inputs respectively. Its output Q when clock pulses are applied will be:

- (A) permanently 0

- (B) permanently 1

- (C) fixed 0 or 1

- (D) complementing with every clock pulse

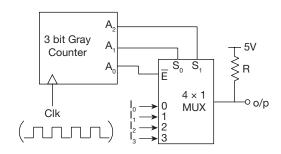

- **25.** A 3 bit gray counter is used to control the output of the multiplexer as shown in figure, the initial state of the counter is 000. The output is pulled high, the output of the circuit follows the sequence

- (D)  $1, I_0, 1, I_1, I_2, 1, I_3, 1, I$

| Answer Keys  |              |              |              |              |             |       |              |              |              |

|--------------|--------------|--------------|--------------|--------------|-------------|-------|--------------|--------------|--------------|

| 1. D         | <b>2.</b> D  | <b>3.</b> C  | <b>4.</b> D  | 5. D         | <b>6.</b> A | 7. D  | <b>8.</b> A  | <b>9.</b> C  | <b>10.</b> B |

| 11. A        | 12. D        | <b>13.</b> B | 14. C        | 15. D        | 16. D       | 17. D | <b>18.</b> B | <b>19.</b> B | <b>20.</b> A |

| <b>21.</b> B | <b>22.</b> D | <b>23.</b> B | <b>24.</b> D | <b>25.</b> B |             |       |              |              |              |

### HINTS AND EXPLANATIONS

1. All flip flops have J = K = 1, so all are toggle switches The output of flip flop is connected to rising edge clk input of next flip flop, so Down counter. clk input is given to flip flop *A* (LSB). Preset is active high, so as preset = 1, all flip flops get 111, so AND gate o/p = 1, when A = 1, B = 0, C = 0 as

$A, \overline{B}, \overline{C}$  are inputs, so the CBA = 001, modulus = 111 - 001 = 6. Choice (D)

So race around condition occurs when A = 1, clk = 1.

Choice (D)

**3.** When two counters are connected in cascade, the resultant modulus is the multiplication of the individual modulus.

So 3 counters are connected so resultant modulus =  $4 \times 4 \times 4 = 64$ . Choice (C)

**4.** JK flip flop works as *T* flip flop if J = K = TFor *D* flip flop  $Q_{n+1} = D$ ,  $Q_{n+1} = T \oplus Q_n$  (*T* flip flop) So by taking  $D = T \oplus Q_n$  we get *T* flip flop.

5. *n* bit binary UP counter counts in Binary sequence, so same binary sequence is applied to Demultiplexer, so input I=1, will be at output in sequence, for 3 bit example.

| $Q_2 Q_1 Q_0$ | $S_2 S_1 S_0$ | <i>Y</i> <sub>0</sub> <i>Y</i> <sub>1</sub> <i>Y</i> <sub>2</sub> <i>Y</i> <sub>7</sub> |

|---------------|---------------|-----------------------------------------------------------------------------------------|

| 000           | 000           | 1 0 0 0                                                                                 |

| 001           | 001           | 0100                                                                                    |

| 010           | 010           | 0 0 1 0                                                                                 |

It works like a module  $2^n$  ring counter. Choice (D)

6. For *D* flip flop whatever input we apply, same output we get after clk pulse

Choice (A)

7. The frequency of  $Q_1 = \frac{fclk}{2}$

Frequency of

$$Q_1 = \frac{\frac{jclk}{2}}{2} = \frac{jclk}{4}$$

Frequency of

$$Q_2 = \frac{fclk}{2} = \frac{fclk}{8}$$

Frequency of

$$Q_3 = \frac{fclk}{16}$$

Frequency of

$$Q_4 = \frac{fclk}{32} = \frac{128}{32} = 4 \text{ kHz}$$

Frequency of

$$Q_5 = \frac{fclk}{64}$$

Choice (D)

8. The given *XY* flip flop truth table is

| <b>X</b> Y <b>Q</b> <sub>n</sub> | <b>Q</b> <sub>n+1</sub> |

|----------------------------------|-------------------------|

| 0 0 0                            | 0                       |

| 0 0 1                            | 1                       |

| 0 1 0                            | 1                       |

| 0 1 1                            | 1                       |

| 1 0 0                            | 0                       |

| 101                              | 0                       |

| 1 1 0                            | 1                       |

| 111                              | 0                       |

$Q_{n+1} = \bar{X}Q_n + Y\bar{Q}_n$

The characteristic equation of *D* flip flop is  $Q_{n+1} = D$ , This has to work like above *XY* flip flop. By equating  $Q_{n+1} = D = \overline{X}Q_n + Y\overline{Q}_n$ . Choice (A)

9. A = 01, B = 10, alternate states when X = 0

When X = 1, A, B go to state C = 11 as long as X = 1, C will remain in same state

When X = 0, C will return to state A = 01 Choice (C)

**10.** Let us consider states as *AB* if initially state of the circuit is 00 (reset)

| Clk | AB | T <sub>A</sub> | Т <sub>в</sub>       |                            |

|-----|----|----------------|----------------------|----------------------------|

| CIK | AD | (A + B)        | (A <sup>1</sup> + B) |                            |

| 0   | 00 | 0              | 1                    | If initially at 00 state,  |

| 1   | 01 | 1              | 1                    | after 3 Clk pulses it      |

| 2   | 10 | 1              | 0                    | comes back to same         |

| 3   | 00 |                |                      | state 00.                  |

| 0   | 11 | 1              | 1                    | If initial state is 11, it |

| 1   | 00 |                |                      | goes to 00 state after     |

|     |    |                |                      | clock pulse                |

Choice (B)

11. Given  $f(a, b, c) = a^{1}b + b^{1}c + ac^{1}$   $= a^{1}b + (a + a^{1})b^{1}c + ac^{1}$   $= a^{1}b + a^{1}b^{1}c + ab^{1}c + ac^{1}$   $= a^{1}[b + b^{1}c] + a[b^{1}c + c^{1}]$   $= a^{1}[b + c] + a[b^{1} + c^{1}]$ By comparing this equation with output of 2 × 1 multiplexer

$$Y = I_0 \overline{S} + l_1 S = I_0 \overline{a} + I_1 a = [b + c]a^1 + [\overline{bc}]a$$

Gate 1 is OR gate, gate 2 is NAND gate.

Choice (A)

- 12. For multiplexer P,  $Y = I_0$ ,  $I_0\overline{S} + I_1S = a^1b^1 + 0 \cdot b$ For mux, Q,  $Y = a^1b^1 + b^1 \cdot b = a^1b^1$ For mux, R,  $Y = b^1.b^1 + a^1 \cdot b = a^1 + b^1 = (ab)^1$ For mux, S,  $Y = 1 \cdot a^1 + b^1 \cdot a = a^1 + b^1 = (ab)^1$ So, R, S implement NAND gate P, Q implements NOR gate. Choice (D)

- **13.** The demultiplexer output  $Y_0 = I\overline{S}_2\overline{S}_1\overline{S}_0$

$$Y_{1} = IS_{2}S_{1}S_{0}$$

$$Y_{2} = I\overline{S}_{2}S_{1}\overline{S}_{0}$$

$$Y_{3} = IS_{2}\overline{S}_{1}\overline{S}_{0}.....etc$$

$$f(a, b, c, d) = Y_{0} + Y_{1} + Y_{6} + Y_{7}$$

$$= ab^{1}c^{1}d^{1} + ab^{1}c^{1}d + abcd^{1} + abcd$$

$$= ab^{1}c^{1} + abc$$

$$= a[b \odot c]$$

Choice (B)

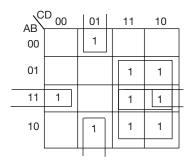

For 8 × 1 multiplexer output

14. For  $8 \times 1$  multiplexer output  $Y = l_0 \overline{S}_2 \overline{S}_1 \overline{S}_0 + I_1 \overline{S}_2 \overline{S}_1 S_0 + I_2 \overline{S}_2 S_1 \overline{S}_0 + I_3 \overline{S}_2 S_1 S_0$   $+ I_4 S_2 \overline{S}_1 \overline{S}_0 + I_5 S_2 \overline{S}_1 S_0 + I_6 S_2 S_1 \overline{S}_0 + I_7 S_2 S_1 S_0$   $= \overline{A} \overline{B} \overline{C} D + 0 + 0 + \overline{A} \overline{B} C + A \overline{B} \overline{C} D + A \overline{B} C$   $+ A \overline{B} \overline{C} \overline{D} + A \overline{B} C$

$$= \sum m(1, 6, 7, 9, 10, 11, 12, 14, 15)$$

$Y = \overline{B}\overline{C}D + AB\overline{D} + BC + AC$

Choice (C)

# 3.16 | Digital Logic Test 2

- **15.** The input  $D = \overline{A \cdot S} = \overline{A} + \overline{S}$ This NAND gate is replaced by OR gate So *A* input should be complemented (to  $\overline{Q}$ ) and *S* input should be complemented. Choice (D)

- 16. NAND gate output = 0<br/>When two inputs are 1.<br/>Only at last clk pulse  $X_1 = X_2 = 1$ <br/>So Y = 0, remaining cases Y = 1,Choice (D)

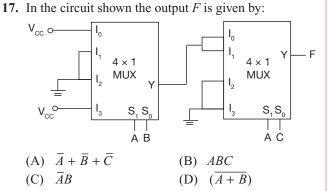

- 17. Output of 1<sup>st</sup> multiplexer is  $Y = I_0 \overline{A}\overline{B} + I_1 \overline{A}B + I_2 A\overline{B} + I_3 AB$   $= \overline{A}\overline{B} + AB = A \odot B$ Output of 2<sup>nd</sup> multiplexer is  $Y = (A \odot B) \overline{A}\overline{C} + (A \odot B) \overline{A} C + 0 \cdot A\overline{C} + 0 \cdot AC$   $= (A \odot B) [\overline{A}\overline{C} + \overline{A}C] = (\overline{A}\overline{B} + AB)\overline{A}$   $= \overline{A}\overline{B} = (\overline{A + B})$ Choice (D)

- 18. Choice (B)

- **19.** If two 2's complement has to be calculated we require two states.

| (Inputs)           | 0                  | 1                  |  |

|--------------------|--------------------|--------------------|--|

| Q <sub>0</sub> (0) | Q <sub>0</sub> , 0 | Q <sub>1</sub> , 1 |  |

| Q <sub>1</sub> (1) | Q <sub>1</sub> , 1 | Q <sub>1</sub> ,0  |  |

We can get 2's complement from LSB, by considering all zero's and the first 1 as it is, there after complementing 0's and 1's. Choice (B)

20.

| Clk | States | Input |

|-----|--------|-------|

|     | ΡQ     | ΤD    |

| 0   | 0 1    | 10    |

| 1   | 10     | 11    |

| 2   | 0 1    | 10    |

| 3   | 10     | 11    |

Choice (A)

**21.** The given circuit is an asynchronous counter (ripple counter) states will change in Binary sequence. Q is connected to rising edge clk pulse so down counter, so sequence is 00, 11, 10, 01, 00 ... Choice (B)

- **22.** By observing sequence  $0000 \rightarrow 1000 \rightarrow 1100 \rightarrow 1110$  $\rightarrow 1111 \rightarrow 0111 \rightarrow 0011 \rightarrow 0001 \rightarrow 0000$ It is twisted ring counter. Choice (D)

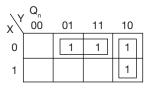

- 23. Output of 1<sup>st</sup> multiplexer  $Y = I_0 \overline{S} + I_1 S = x^1 z^1 + yz$ Output of 2<sup>nd</sup> multiplexer  $Y = I_0 \overline{S} + I_1 S$   $= (x^1 z^1 + yz) (y^1)^1 + xy^1$   $= x^1 yz^1 + yz + xy^1 = \sum m (2, 3, 4, 5, 7)$  x yz 00 01 11 10 1 f = xy^1 + x^1y + yz x yz 00 01 11 10 f = xy^1 + x^1y + xz

Choice (B)

**24.** Q is connected to R,  $\overline{Q}$  to S input

So

$$Q_{n+1} = S + \overline{R}Q_n = Q_n + Q_n \cdot Q_n$$

So  $Q_{n+1} = \overline{Q}_n$  so next state is complement of present state. Choice (D)

| 1 | 5  |  |

|---|----|--|

| 4 | э. |  |

| A <sub>2</sub> A <sub>1</sub> A | D E | S <sub>1</sub> S <sub>0</sub> | o/p            |

|---------------------------------|-----|-------------------------------|----------------|

| 0 0 0                           | 0 0 | 0 0                           | I <sub>0</sub> |

| 0 0 1                           | 1 1 | 0 0                           | 1              |

| 0 1 1                           | 1   | 0 1                           | 1              |

| 010                             | 0 0 | 0 1                           | I <sub>1</sub> |

| 1 1 (                           | 0 0 | 1 1                           | l <sub>3</sub> |

| 1 1 1                           | 1   | 1 1                           | 1              |

| 1 0 1                           | 1 1 | 1 0                           | 1              |

| 1 0 0                           | ) 0 | 1 0                           | l <sub>2</sub> |

| 0 0 0                           | ) 0 | 0 0                           | I <sub>0</sub> |

Enable is active low, when E = 1, the output is logic 1 When E = 0, output is from multiplexer. Choice (B)